04基本IO口操作

CC2530端口资源:三个端口,表示为 P0、P1 和 P2。P0 和 P1 是完全的 8 位端口,而 P2 仅有 5 位可用

CC2530的IO口的一些功能:

通用IO口、外设IO口(定时器、USART、ADC)

输入引脚、输出引脚

当输入时,上拉、下拉、高阻态(三态)

寄存器简略介绍:

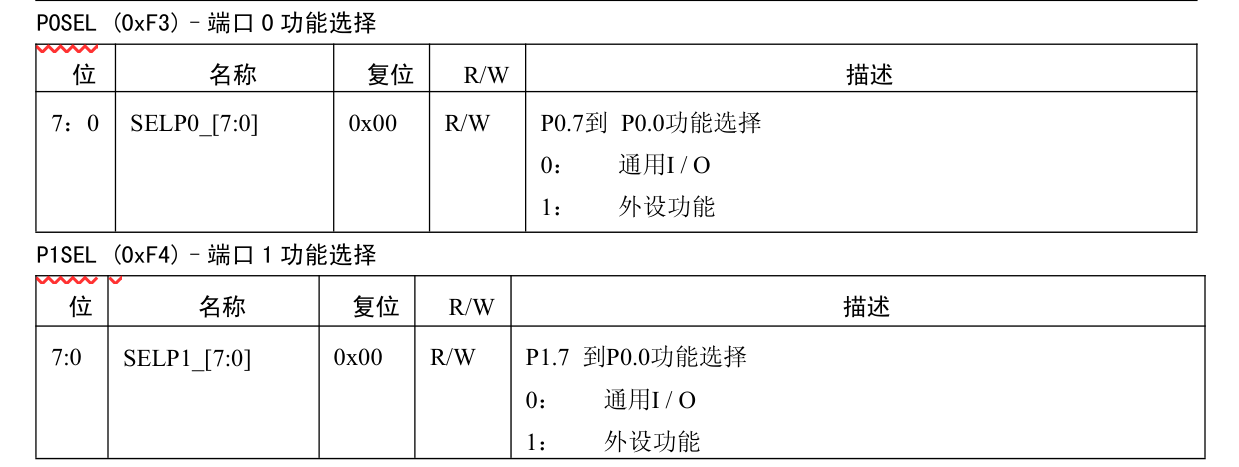

PxSEL 置0为通用I/O口,置1为专用功能

PxDIR 置0为输入模式,置1为输出模式

PxINP 置0为上/下拉模式,置1位三态模式(高阻态)

1.对应P1INP和P0INP来说,0~7位均满足上述规则

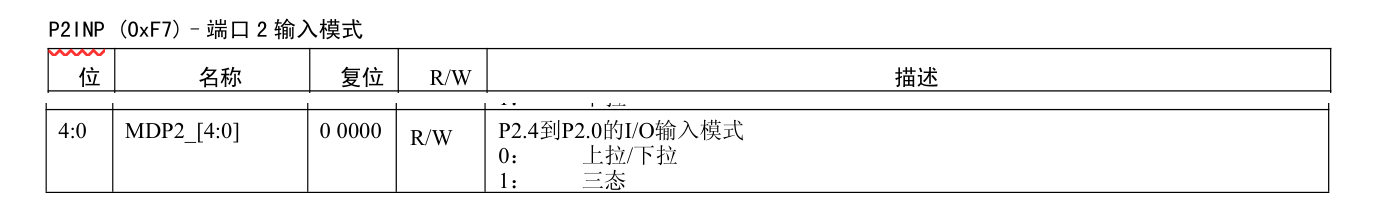

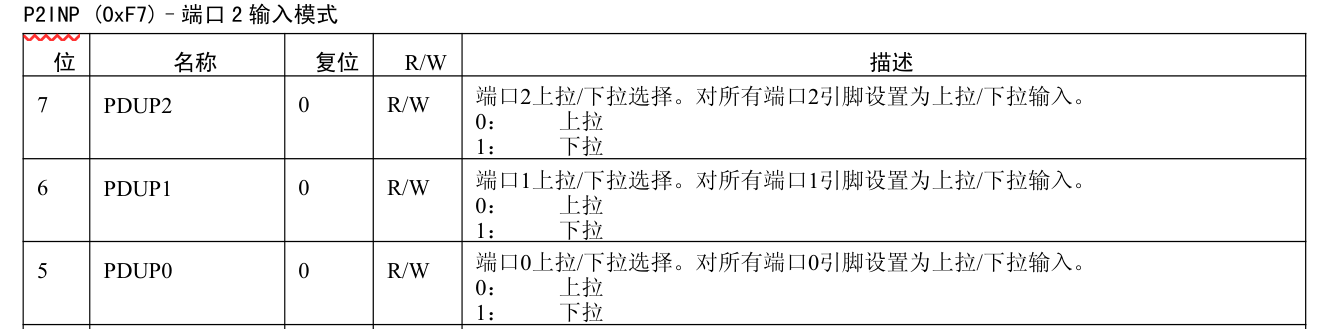

2.对于P2INP来说,0 ~ 4位满足上述规则,5 ~ 7为专用功能,即5、6、7分别用来控制P0、P1、P2组端口的上下拉模式(0上拉、1下拉)

端口配置寄存器

PxSEL寄存器

寄存器 PxSEL,其中 x 为端口的标号 0~2,用来设置端口的每个引脚为通用 I/O(0) 或者是外部设备I/O(1)。

默认上电后为普通IO口上拉输入

P2组只有5个IO口,但是P2_1和P2_2是用于下载程序用的,所以这两个IO不需要配置

因此P2SEL的低3位分别对应P2_0、P2_3 、P2_4

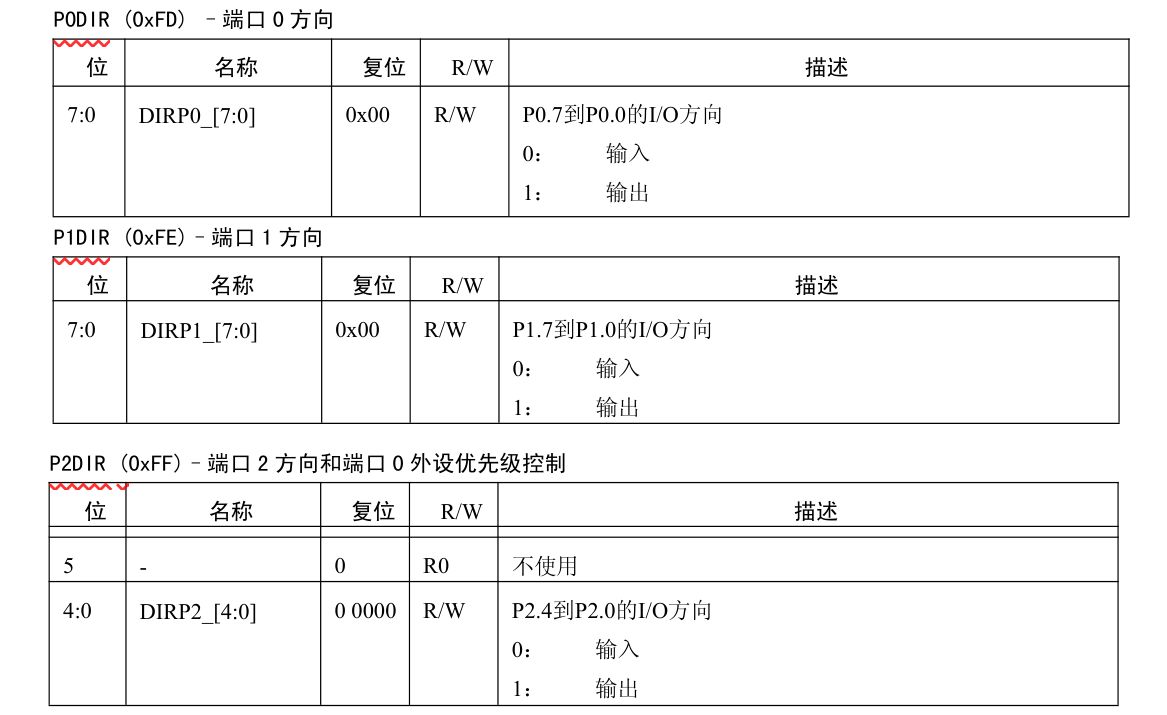

PxDIR寄存器

在任何时候,要改变一个端口引脚的方向,就使用寄存器 PxDIR 来设置每个端口引脚为输入或输出

如果使用输出功能,则不需要使用PxINP寄存器

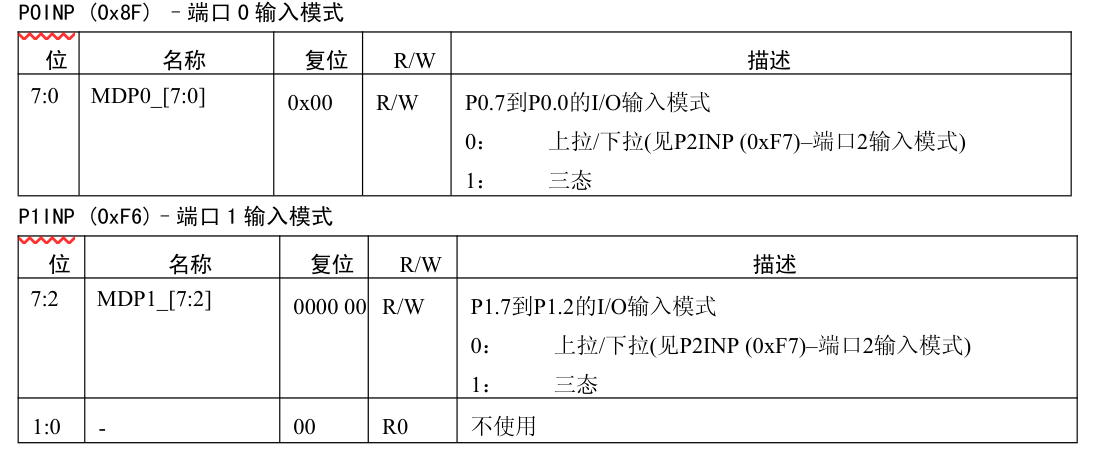

PxINP寄存器

设置通用IO端口的输入模式:上拉、下拉或三态(高阻态)

-

选择输入端口是否为高阻态

-

使用P0INP、P1INP以及P2INP的0~4位

-

需要注意的是,P1_0 和 P1_1 没有上拉/下拉功能

-

-

如果选择了上下拉模式,使用P2INP的5~7位确定到底为上拉还是下拉

-

P2_5:确定P0口

-

P2_6:确定P1口

-

P2_7:确定P2口

-

寄存器使用

对某一位置1,使用或运算【|】

对某一位置0,使用与运算【&】

例1:设置P1_0口为通用输出IO口

1 | P1SEL &= ~0x01; //P1.0设置为通用I/O口 |

例2:设置P0_6口为通用上拉输入IO口

1 | P0SEL &= ~0x40;//P0.6设置为通用I/O口 |

例3:结合例1和例2来实现监测外部P0_6口的高低电平,高电平点亮LED灯(P1_0)

实验现象:拔出跳线帽灯亮,插上跳线帽灯灭

1 |

|